The art of the language VM, or Machine-generating virtual machine code, or Almost zero overhead with almost zero assembly, or My virtual machine is faster than yours

Luca Saiu positron@gnu.org http://ageinghacker.net

GNU Project

GNU Hackers' Meeting 2017 Knüllwald-Niederbeisheim, Germany August 25<sup>th</sup> 2017

About these slides: Copyright © Luca Saiu 2017, released under the CC BY-SA 4.0 license. Updated version, last changed on 2017-10-02. The master copy is at http://ageinghacker.net/talks/

## Introduction and history

My main long-term project is GNU epsilon. It's a programming language, meant to be efficient, but:

- very "dynamic" in certain execution phases

- written in itself, bootstrapped

- Too slow.

## Introduction and history

My main long-term project is GNU epsilon. It's a programming language, meant to be efficient, but:

- very "dynamic" in certain execution phases

- written in itself, bootstrapped

- Too slow.

So I wrote a canonical threaded-code VM.

- speedup 4-6x

- Too little.

So I made a separate repository to experiment with language VMs.

- tried techniques from scientific papers (many by Anton Ertl and the other GForth people)

- added ideas of my own

A new project, independent from epsilon

Basics Specialization Replication No-threading Closing

## Introduction and history

My main long-term project is GNU epsilon. It's a programming language, meant to be efficient, but:

- very "dynamic" in certain execution phases

- written in itself, bootstrapped

- Too slow.

So I wrote a canonical threaded-code VM.

- speedup 4-6x

- Too little.

So I made a separate repository to experiment with language VMs.

- tried techniques from scientific papers (many by Anton Ertl and the other GForth people)

- added ideas of my own

• it got completely out of hand new project, independent from eps

Basics Specialization Replication No-threading Closing

## Introduction and history

My main long-term project is GNU epsilon. It's a programming language, meant to be efficient, but:

- very "dynamic" in certain execution phases

- written in itself, bootstrapped

- Too slow.

So I wrote a canonical threaded-code VM.

- speedup 4-6x

- Too little.

So I made a separate repository to experiment with language VMs.

- tried techniques from scientific papers (many by Anton Ertl and the other GForth people)

- added ideas of my own

- it got completely out of hand

## Why you should care

#### Interpreters are common:

- programming languages

- application scripting

- shells

- regular expressions. . .

We are getting used to unacceptably bad performance.

I will present my new software, but first I need to describe the problem it solves. This will take a while.

## Why you should care

#### Interpreters are common:

- programming languages

- application scripting

- shells

- regular expressions. . .

• We are getting used to unacceptably bad performance.

I will present my new software, but first I need to describe the problem it solves. This will take a while.

## Why you should care

#### Interpreters are common:

- programming languages

- application scripting

- shells

- regular expressions. . .

• We are getting used to unacceptably bad performance.

I will present my new software, but first I need to describe the problem it solves. This will take a while.

# Our running example — at first in C

Count down from two billion (here meaning  $2 \cdot 10^9$ ):

```

c

int

main (void)

{

long i;

for (i = 2000000000; i != 0; i --)

/* Do nothing */;

return 0;

}

```

...does this program really count down?

## Our running example — at first in C

Count down from two billion (here meaning  $2 \cdot 10^9$ ):

```

int

main (void)

{

long i;

for (i = 2000000000; i != 0; i --)

/* Do nothing */;

return 0;

}

```

...does this program really count down?

## Our running example — at first in C, now actually counting

Count down from  $2 \cdot 10^9$  without optimizing away the entire loop:

```

C (with GNU extensions)

int

main (void)

{

long i;

for (i = 2000000000; i != 0; i --)

asm volatile ("" : : "r" (i)); // pretend to use i

return 0;

}

```

(We still want most GCC optimizations!)

[Demo: the down-counter in a few languages

# Our running example — at first in C, now actually counting

Count down from  $2 \cdot 10^9$  without optimizing away the entire loop:

```

C (with GNU extensions)

int

main (void)

{

long i;

for (i = 2000000000; i != 0; i --)

asm volatile ("" : : "r" (i)); // pretend to use i

return 0;

}

```

(We still want most GCC optimizations!)

Demo: the down-counter in a few languages

## Our running example — at first in C, now actually counting

Count down from  $2 \cdot 10^9$  without optimizing away the entire loop:

```

C (with GNU extensions)

int

main (void)

{

long i;

for (i = 2000000000; i != 0; i --)

asm volatile ("" : : "r" (i)); // pretend to use i

return 0;

}

```

(We still want most GCC optimizations!)

[Demo: the down-counter in a few languages]

Example AST Linear switch Threading Args Stacks

### You can play with the sources

I will (quickly) show some interpreters written in C.

In case you want to play with the examples yourself, the little programs I'm showing here are on my server:

These are naif C programs showing how interpreters work; the C files in c-examples/ are not part of my new project.

## How simple interpreters work

The interpreted program is a data structure in memory. "find the next point in the interpreted program, execute it, repeat from start"

How to *dispatch* ["dispatch": moving from a VM program point to another]:

- Abstract Syntax Tree (AST) interpreters

- Linear programs

- switch dispatching

- direct threading

- . . .

How to access data:

- associative data structures (alists, hash tables)

- VM registers

- stack

## How simple interpreters work

The interpreted program is a data structure in memory. "find the next point in the interpreted program, execute it, repeat from start"

How to *dispatch* ["dispatch": moving from a VM program point to another]:

- Abstract Syntax Tree (AST) interpreters

- Linear programs

- switch dispatching

- direct threading

- . . .

#### How to access data

- associative data structures (alists, hash tables)

- VM registers

- stack

## How simple interpreters work

The interpreted program is a data structure in memory. "find the next point in the interpreted program, execute it, repeat from start"

How to *dispatch* ["dispatch": moving from a VM program point to another]:

- Abstract Syntax Tree (AST) interpreters

- Linear programs

- switch dispatching

- direct threading

- . . . .

#### How to access data:

- associative data structures (alists, hash tables)

- VM registers

- stacks

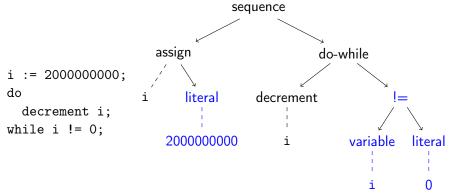

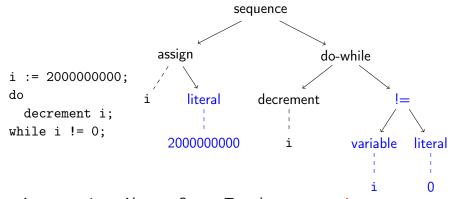

### Our down-counter as an Abstract Syntax Tree

```

:= 2000000000;

do

decrement i;

while i != 0;

```

A program is an Abstract Syntax Tree data structure in memory: heap-allocated structs and unions with lots of pointers. Each node has an enum field to distinguish its kind.

Blue: expression node; dashed line: child is a struct field of parent; black

### Our down-counter as an Abstract Syntax Tree

A program is an Abstract Syntax Tree data structure in memory: heap-allocated structs and unions with lots of pointers. Each node has an enum field to distinguish its kind.

[Blue: expression node; dashed line: child is a struct field of parent; black arrow: parent contains pointer to child.]

### Our down-counter as an Abstract Syntax Tree

A program is an Abstract Syntax Tree data structure in memory: heap-allocated structs and unions with lots of pointers. Each node has an enum field to distinguish its kind.

[Blue: expression node; dashed line: child is a struct field of parent; black arrow: parent contains pointer to child.]

### Abstract Syntax Tree interpreter: expression

As each complex AST has sub-ASTs recursion is natural. AST data structures are easy to define in Lisp and ML, a little less pretty in C.

```

long

interpret_expr (const struct expr *e, const long *vars) {

switch (e->expr_case) {

case expr_variable:

return vars [e->var_index];

case expr_constant:

return e->cnst:

case expr_is_different:

return ( interpret_expr (e->sub1, vars)

!= interpret_expr (e->sub2, vars));

default:

error ();

```

#### Abstract Syntax Tree interpreter: statement

```

void interpret_stmt (const struct stmt *s, long *vars) {

switch (s->stmt case) {

case stmt_sequence:

interpret_stmt (s->sub1, vars);

interpret_stmt (s->sub2, vars);

break:

case stmt_assign:

vars [s->var_index] = interpret_expr (s->assigned_expr, vars);

break:

case stmt decrement:

vars [s->var_index] --;

break:

case stmt dowhile:

interpret_stmt (s->body, vars);

if (interpret_expr (s->guard, vars))

interpret_stmt (s, vars);

break:

default: error ():

```

## AST interpreter performance

• pointer chasing (load latency  $\sim 3\tau$  on L1d hit!)

## AST interpreter performance

- ullet pointer chasing (load latency  $\sim 3 au$  on L1d hit!)

- ullet many conditionals, often multi-way (mispredict penalty  $\sim 15 au$ , per conditional branch!)

## AST interpreter performance

- ullet pointer chasing (load latency  $\sim 3 au$  on L1d hit!)

- ullet many conditionals, often multi-way (mispredict penalty  $\sim$  15au, per conditional branch!)

- variable lookup slow (not shown in my sample code before)

## AST interpreter performance

- ullet pointer chasing (load latency  $\sim 3 au$  on L1d hit!)

- ullet many conditionals, often multi-way (mispredict penalty  $\sim$  15au, per conditional branch!)

- variable lookup slow (not shown in my sample code before)

- recursion, often non-tail

## AST interpreter performance

- ullet pointer chasing (load latency  $\sim 3 au$  on L1d hit!)

- ullet many conditionals, often multi-way (mispredict penalty  $\sim 15 au$ , per conditional branch!)

- variable lookup slow (not shown in my sample code before)

• recursion, often non-tail

### A good language to interpret

What is normally called a language "Virtual Machine" is an interpreter for a lower-level linear program:

- the program to interpret is stored as a contiguous array in hardware memory

- no nesting: no statements with sub-statements or expressions with sub-expressions

- no expressions, no variables

- assembly-like feel: registers or stacks, explicit jumps

I'll show you a linear-program interpreter written in C.

### A good language to interpret

What is normally called a language "Virtual Machine" is an interpreter for a lower-level linear program:

- the program to interpret is stored as a contiguous array in hardware memory

- no nesting: no statements with sub-statements or expressions with sub-expressions

- no expressions, no variables

- assembly-like feel: registers or stacks, explicit jumps

I'll show you a linear-program interpreter written in C.

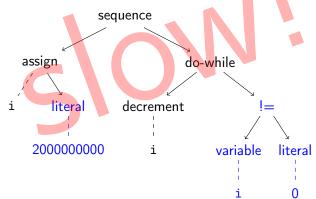

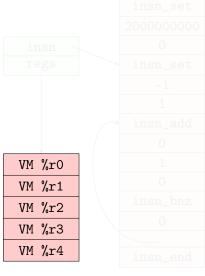

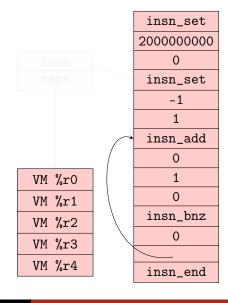

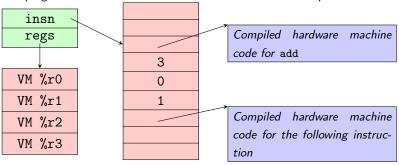

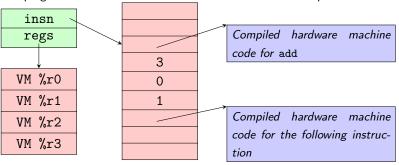

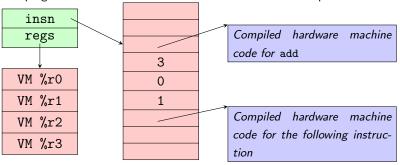

#### The down-counter as a linear program to be interpreted

- VM registers are an array in hardware memory.

- The VM program is an array in hardware memory.

- Only the interpreter's automatic C variables are in hardware registers

### The down-counter as a linear program to be interpreted

- VM registers are an array in hardware memory.

- The VM program is ar array in hardware memory.

- Only the interpreter's automatic C variables are in hardware registers.

## The down-counter as a linear program to be interpreted

- VM registers are an array in hardware memory.

- The VM program is an array in hardware memory.

- Only the interpreter's automatic C variables are in hardware

## The down-counter as a linear program to be interpreted

- VM registers are an array in hardware memory.

- The VM program is an array in hardware memory.

- Only the interpreter's automatic C variables are in hardware registers.

## The simplest linear-program interpreter

#### What's the C type of insn\_set, insn\_add, insn\_bnz, insn\_end?

## The simplest linear-program interpreter

What's the C type of insn\_set, insn\_add, insn\_bnz, insn\_end?

- It's an enum insn: essentially an integer.

## The simplest linear-program interpreter

What's the C type of insn\_set, insn\_add, insn\_bnz, insn\_end?

- It's an enum insn: essentially an integer.

- There are also pointers in the VM program array from an element to another....

### The simplest linear-program interpreter

What's the C type of insn\_set, insn\_add, insn\_bnz, insn\_end?

- It's an enum insn: essentially an integer.

- There are also pointers *in* the VM program array from an element to another...

- Linear-program interpreters work best with word-sized data: objects as wide as a hardware register. unions are useful for this:

```

union value

{

enum insn in;

long i; // or another integer type of the right width

union value *p;

};

```

This interpretation style is called switch dispatching.

# The simplest linear-program interpreter

What's the C type of insn\_set, insn\_add, insn\_bnz, insn\_end?

- It's an enum insn: essentially an integer.

- There are also pointers in the VM program array from an element to another...

- Linear-program interpreters work best with word-sized data: objects as wide as a hardware register. unions are useful for this:

```

C

union value

enum insn in;

long i; // or another integer type of the right width

union value *p;

};

```

This interpretation style is called switch dispatching.

### Problems with switch-dispatching

### Problems with switch-dispatching

- switch is somewhat inefficient (range checking)

- The CPU branch target predictor can't work well: one jumping instruction with many possible targets, complex repetition patterns.

- Every VM instruction ends with another jump to the one shared switch

### Problems with switch-dispatching

- switch is somewhat inefficient (range checking)

- The CPU branch target predictor can't work well: one jumping instruction with many possible targets, complex repetition patterns.

- Every VM instruction ends with another jump to the one shared switch.

### Problems with switch-dispatching

- switch is somewhat inefficient (range checking)

- The CPU branch target predictor can't work well: one jumping instruction with many possible targets, complex repetition patterns.

- Every VM instruction ends with another jump to the one shared switch.

### Problems with switch-dispatching

- switch is somewhat inefficient (range checking)

- The CPU branch target predictor can't work well: one jumping instruction with many possible targets, complex repetition patterns.

- Every VM instruction ends with another jump to the one shared switch.

### Computed goto

# GCC introduced the C extension called computed goto or labels-as-values:

- The expression && label, of type void \*, evaluates to the address of the hardware machine instruction where the labeled code begins; you can store the address and jump to it later.

- I he statement goto \*expr jumps to the result of the evaluation of expr.

We can use pointers to native code instead of instead of enums in the VM program, at the beginning of every VM instruction. This is called direct-threaded code (nothing to do with multi-threading).

### Computed goto

GCC introduced the C extension called computed goto or labels-as-values:

- The expression && label, of type void \*, evaluates to the address of the hardware machine instruction where the labeled code begins; you can store the address and jump to it later.

- I he statement goto \*expr jumps to the result of the evaluation of expr.

We can use pointers to native code instead of instead of enums in the VM program, at the beginning of every VM instruction. This is called direct-threaded code (nothing to do with multi-threading).

### Computed goto

GCC introduced the C extension called computed goto or labels-as-values:

- The expression && label, of type void \*, evaluates to the address of the hardware machine instruction where the labeled code begins; you can store the address and jump to it later.

- The statement goto \*expr jumps to the result of the evaluation of expr.

We can use pointers to native code instead of instead of enums in the VM program, at the beginning of every VM instruction. This is called direct-threaded code (nothing to do with multi-threading).

### Computed goto

GCC introduced the C extension called computed goto or labels-as-values:

- The expression && label, of type void \*, evaluates to the address of the hardware machine instruction where the labeled code begins; you can store the address and jump to it later.

- The statement goto \*expr jumps to the result of the evaluation of expr.

We can use pointers to native code instead of instead of enums in the VM program, at the beginning of every VM instruction. This is called direct-threaded code (nothing to do with multi-threading).

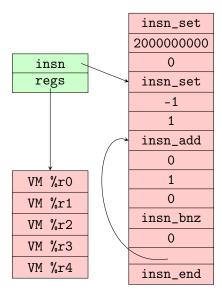

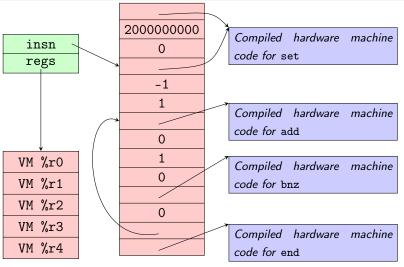

### The down-counter program for a direct-threaded VM

Instead of an enum identifier each VM instruction in the VM program begins with a pointer to its native code.

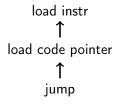

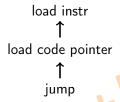

### Direct-threaded interpretation

- interpreting the VM instruction pointed by a C pointer p is trivial:

- there's no switch

- no infinite loop or jump to a shared conditional: each VM instruction "falls thru" to the next:

- move insn forward

- load the next VM instruction code pointer from it

- goto \* to the code pointer

- Many different jumping hardware instructions: less bad for the hardware branch target predictor

- (also, still as compact in memory as switch-dispatching: useful for small embedded systems, but not particularly for GNU)

### Direct-threaded interpretation

- interpreting the VM instruction pointed by a C pointer p is trivial: goto \*p;

- there's no switch

- no infinite loop or jump to a shared conditional: each VM instruction "falls thru" to the next:

- move insn forward

- load the next VM instruction code pointer from it

- goto \* to the code pointer

- Many different jumping hardware instructions: less bad for the hardware branch target predictor

- (also, still as compact in memory as switch-dispatching: useful for small embedded systems, but not particularly for GNU)

### Direct-threaded interpretation

- interpreting the VM instruction pointed by a C pointer p is trivial: goto \*p;

- there's no switch

- no infinite loop or jump to a shared conditional: each VM instruction "falls thru" to the next:

- move insn forward

- load the next VM instruction code pointer from it

- goto \* to the code pointer

- Many different jumping hardware instructions: less bad for the hardware branch target predictor

- (also, still as compact in memory as switch-dispatching: useful for small embedded systems, but not particularly for GNU)

### Direct-threaded interpretation

- interpreting the VM instruction pointed by a C pointer p is trivial: goto \*p;

- there's no switch

- no infinite loop or jump to a shared conditional: each VM instruction "falls thru" to the next:

- move insn forward

- load the next VM instruction code pointer from it

- goto \* to the code pointer

- Many different jumping hardware instructions: less bad for the hardware branch target predictor

- (also, still as compact in memory as switch-dispatching: useful for small embedded systems, but not particularly for GNU)

### Direct-threaded interpretation

- interpreting the VM instruction pointed by a C pointer p is trivial: goto \*p;

- there's no switch

- no infinite loop or jump to a shared conditional: each VM instruction "falls thru" to the next:

- move insn forward

- load the next VM instruction code pointer from it

- goto \* to the code pointer

- Many different jumping hardware instructions: less bad for the hardware branch target predictor

- (also, still as compact in memory as switch-dispatching: useful for small embedded systems, but not particularly for GNU)

### Direct-threaded interpretation

- interpreting the VM instruction pointed by a C pointer p is trivial: goto \*p;

- there's no switch

- no infinite loop or jump to a shared conditional: each VM instruction "falls thru" to the next:

- move insn forward

- load the next VM instruction code pointer from it

- goto \* to the code pointer

- Many different jumping hardware instructions: less bad for the hardware branch target predictor

- (also, still as compact in memory as switch-dispatching: useful for small embedded systems, but not particularly for GNU)

### Direct-threaded interpretation

- interpreting the VM instruction pointed by a C pointer p is trivial: goto \*p;

- there's no switch

- no infinite loop or jump to a shared conditional: each VM instruction "falls thru" to the next:

- move insn forward

- load the next VM instruction code pointer from it

- goto \* to the code pointer

- Many different jumping hardware instructions: less bad for the hardware branch target predictor

- (also, still as compact in memory as switch-dispatching: useful for small embedded systems, but not particularly for GNU)

### Direct-threaded interpretation

- interpreting the VM instruction pointed by a C pointer p is trivial: goto \*p;

- there's no switch

- no infinite loop or jump to a shared conditional: each VM instruction "falls thru" to the next:

- move insn forward

- load the next VM instruction code pointer from it

- goto \* to the code pointer

- Many different jumping hardware instructions: less bad for the hardware branch target predictor

- (also, still as compact in memory as switch-dispatching: useful for small embedded systems, but not particularly for GNU)

### Direct-threaded interpretation

- interpreting the VM instruction pointed by a C pointer p is trivial: goto \*p;

- there's no switch

- no infinite loop or jump to a shared conditional: each VM instruction "falls thru" to the next:

- move insn forward

- load the next VM instruction code pointer from it

- goto \* to the code pointer

- Many different jumping hardware instructions: less bad for the hardware branch target predictor

- (also, still as compact in memory as switch-dispatching: useful for small embedded systems, but not particularly for GNU)

### Direct-threaded interpretation

- interpreting the VM instruction pointed by a C pointer p is trivial: goto \*p;

- there's no switch

- no infinite loop or jump to a shared conditional: each VM instruction "falls thru" to the next:

- move insn forward

- load the next VM instruction code pointer from it

- goto \* to the code pointer

- Many different jumping hardware instructions: less bad for the hardware branch target predictor

- (also, still as compact in memory as switch-dispatching: useful for small embedded systems, but not particularly for GNU)

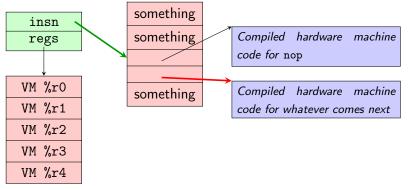

### Direct-threaded fallthru (nop): diagram

The zero-argument VM instruction nop does nothing and just falls thru to the next instruction.

The jump destination address is pointed from memory (red arrow). The green arrow is the pointer insn, already in a hardware register.

There is nothing between the code pointer for nop and the code pointer for the next VM instruction because nop has no arguments.

# Direct-threaded fallthru (nop): code

Here's the source for the VM instruction nop in the direct-threading interpreter:

#### **GNU C**

```

label_nop:

insn ++;  // No args to skip, just the code pointer

goto * insn->label;

```

#### compiled (x86 64)

```

movq 8(%rax), %rdx #insn is in %rax; load (insn + 1)->label addq $8, %rax #advance insn to the next instruction jmpq *%rdx #jump to the address we loaded before

```

GCC has put insn in the hardware register %rax. The load (movq on x86\_64) follows the red arrow, from %rax + 8. The hardware register %rdx is a temporary, holding the address where to jump.

# Direct-threaded fallthru (nop): code

Here's the source for the VM instruction nop in the direct-threading interpreter:

#### **GNU C**

```

label_nop:

insn ++;  // No args to skip, just the code pointer

goto * insn->label;

```

```

compiled (x86_64)

```

```

movq 8(%rax), %rdx #insn is in %rax; load (insn + 1)->label addq $8, %rax #advance insn to the next instruction jmpq *%rdx #jump to the address we loaded before

```

GCC has put insn in the hardware register %rax. The load (movq on x86\_64) follows the red arrow, from %rax + 8. The hardware register %rdx is a temporary, holding the address where to jump.

# Direct-threaded fallthru (nop): code

Here's the source for the VM instruction nop in the direct-threading interpreter:

#### **GNU C**

```

label_nop:

insn ++;  // No args to skip, just the code pointer

goto * insn->label;

```

```

compiled (x86 64)

```

```

movq 8(%rax), %rdx #insn is in %rax; load (insn + 1)->label addq $8, %rax #advance insn to the next instruction jmpq *%rdx #jump to the address we loaded before

```

GCC has put insn in the hardware register %rax. The load (movq on x86\_64) follows the red arrow, from %rax + 8. The hardware register %rdx is a temporary, holding the address where to jump.

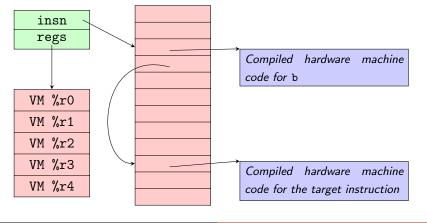

### Direct-threaded unconditional branch (b): diagram

The b VM instruction takes a label as its parameter: the next VM program slot after b's code pointer points to the beginning of the target instruction (another slot in the program containing a code pointer).

### Direct-threaded unconditional branch (b): code

The (one-argument) VM instruction b in the direct-threading interpreter:

```

GNU C

label_b:

insn = insn[1].p;

goto * insn->label;

```

```

compiled (x86 64)

```

Luca Saiu

```

movq 8(%rax), %rax # load jump destination from *(insn + 1)

jmpq *(%rax) # jump indirect via memory: another load

```

The first instruction loads the next insn, still pointing within the program array. The jump-via-memory instruction chases a pointer from it and obtains a pointer into a "blue" box, the hardware instruction where to jump where the target VM instruction begins.

### Direct-threaded unconditional branch (b): code

The (one-argument) VM instruction b in the direct-threading interpreter:

```

GNU C

label_b:

insn = insn[1].p;

goto * insn->label;

```

```

compiled (x86 64)

movq 8(%rax), %rax # load jump destination from *(insn + 1)

jmpq *(%rax)

# jump indirect via memory: another load

```

The first instruction loads the next insn, still pointing within the program array. The jump-via-memory instruction chases a pointer from it and obtains a pointer into a "blue" box, the hardware instruction where to jump where the target VM instruction begins.

### Direct-threaded conditional branch (bnz)

The two-argument VM instruction bnz in the direct-threading interpreter:

```

GNU C

label_bnz:

if (regs[insn[1].i] != 0)

insn = insn[2].p;

else

insn += 3;

goto * insn->label;

```

```

compiled (x86_64, simplified)

movq 8(%rax), %rdx

cmpq $0, -256(%rbp,%rdx,8)

je L

movq 16(%rax), %rax # Like b

jmpq *(%rax)

L: addq $24, %rax # Fallthru

impg *(%rax)

```

Check the condition; if false skip past (je) unconditional branch code. and into fallthru dispatch code.

Lots of hardware branches, depending on memory and on each other

### Direct-threaded conditional branch (bnz)

The two-argument VM instruction bnz in the direct-threading interpreter:

```

GNU C

label_bnz:

if (regs[insn[1].i] != 0)

insn = insn[2].p;

else

insn += 3;

goto * insn->label;

```

```

compiled (x86_64, simplified)

movq 8(%rax), %rdx

cmpq $0, -256(%rbp,%rdx,8)

je L

movq 16(%rax), %rax # Like b

jmpq *(%rax)

L: addq $24, %rax # Fallthru

jmpq *(%rax)

```

Check the condition; if false skip past (je) unconditional branch code, and into fallthru dispatch code.

Lots of hardware branches, depending on memory and on each other

### Direct-threaded conditional branch (bnz)

The two-argument VM instruction bnz in the direct-threading interpreter:

```

GNU C

label_bnz:

if (regs[insn[1].i] != 0)

insn = insn[2].p;

else

insn += 3;

goto * insn->label;

```

```

compiled (x86_64, simplified)

movq 8(%rax), %rdx

cmpq $0, -256(%rbp,%rdx,8)

je  L

movq 16(%rax), %rax # Like b

jmpq *(%rax)

L: addq $24, %rax # Fallthru

jmpq *(%rax)

```

Check the condition; if false skip past (je) unconditional branch code, and into fallthru dispatch code.

Lots of hardware branches, depending on memory and on each other

### Direct-threaded conditional branch (bnz)

The two-argument VM instruction bnz in the direct-threading interpreter:

```

GNU C

label_bnz:

if (regs[insn[1].i] != 0)

insn = insn[2].p;

else

insn += 3;

goto * insn->label;

```

```

compiled (x86_64, simplified)

movq 8(%rax), %rdx

cmpq $0, -256(%rbp,%rdx,8)

je L

movq 16(%rax), %rax # Like b

jmpq *(%rax)

L: addq $24, %rax # Fallthru

jmpq *(%rax)

```

Check the condition; if false skip past (je) unconditional branch code, and into fallthru dispatch code.

Lots of hardware branches, depending on memory and on each other.

### Direct threading dispatch performance

### Direct threading dispatch performance

The real question is whether we can do better, and where the bottleneck is.

Is branching/fallthru the only source of inefficiency?

[Demo: quick timing against switch-dispatching]

### Direct threading dispatch performance

The real question is whether we can do better, and where the bottleneck is.

Is branching/fallthru the only source of inefficiency?

[Demo: quick timing against switch-dispatching]

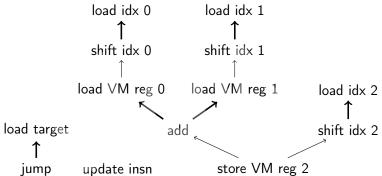

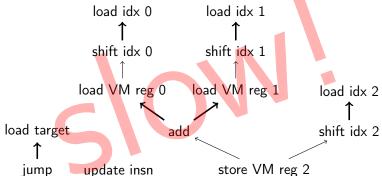

# (Direct-threaded) VM add: "fundamental"/RISC operations

Let's look at how the VM instruction add %r3, %r0, %r1 is represented in the VM program and what it needs to do in terms of hardware "operations":

# (Direct-threaded) VM add: "fundamental"/RISC operations

Let's look at how the VM instruction add %r3, %r0, %r1 is represented in the VM program and what it needs to do in terms of hardware "operations":

- read VM register indices (load from insn[k] obtaining 3, 0, 1)

- read VM input register contents from the VM register array using input indices (load VM register elements %x3, %x0 using indices 3, 0)

- do the actual sum

- write result into VM register array (store into VM %r1 using index 1)

- fallthru: increment-load-iumn as always

Example AST Linear switch Threading Args Stacks Basics Specialization Replication No-threading Closing

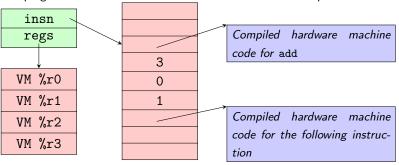

## (Direct-threaded) VM add: "fundamental"/RISC operations

Let's look at how the VM instruction add %r3, %r0, %r1 is represented in the VM program and what it needs to do in terms of hardware "operations":

- read VM register indices (load from insn[k] obtaining 3, 0, 1)

- read VM input register contents from the VM register array using input indices (load VM register elements %r3, %r0 using indices 3, 0)

## (Direct-threaded) VM add: "fundamental"/RISC operations

Let's look at how the VM instruction add %r3, %r0, %r1 is represented in the VM program and what it needs to do in terms of hardware "operations":

- read VM register indices (load from insn[k] obtaining 3, 0, 1)

- read VM input register contents from the VM register array using input indices (load VM register elements %x3, %x0 using indices 3, 0)

- do the actual sum

write result into VM register array (store into VM %r1 using index 1)

fallthru: increment-load-jump, as always

# (Direct-threaded) VM add: "fundamental"/RISC operations

Let's look at how the VM instruction add %r3, %r0, %r1 is represented in the VM program and what it needs to do in terms of hardware "operations":

- read VM register indices (load from insn[k] obtaining 3, 0, 1)

- read VM input register contents from the VM register array using input indices (load VM register elements %x3, %x0 using indices 3, 0)

- do the actual sum

- write result into VM register array (store into VM %r1 using index 1)

- fallthru: increment-load-iumi

# (Direct-threaded) VM add: "fundamental"/RISC operations

Let's look at how the VM instruction add %r3, %r0, %r1 is represented in the VM program and what it needs to do in terms of hardware "operations":

- read VM register indices (load from insn[k] obtaining 3, 0, 1)

- read VM input register contents from the VM register array using input indices (load VM register elements %r3, %r0 using indices 3, 0)

- do the actual sum

- write result into VM register array (store into VM %r1 using index 1)

- fallthru: increment-load-jump, as always

# The VM instruction add (here direct-threaded), compiled

```

compiled (x86_64, simplified)

movq 8(%rax), %rsi

movq 16(%rax), %rdx

addq $32, %rax

movq -8(%rax), %rcx

movq -256(%rbp,%rdx,8), %rdx

addq -256(%rbp,%rsi,8), %rdx # +

movq %rdx, -256(%rbp,%rcx,8)

movq (%rax), %rdx

impo *rdx

```

- the actual addition costs only one hardware instruction (the second addg, in black [which also includes one memory access]).

- Fallthru to the next VM instruction: three hardware instructions (*increment-load-jump*).

- The other five hardware instructions only serve to access VM registers (and on RISCs it's even worse).

## The VM instruction add (here direct-threaded), compiled

```

GNU C

label add:

regs[insn[3].i]

= ( regs[insn[1].i]

+ regs[insn[2].i]);

insn += 4:

goto * insn->label;

```

```

compiled (x86 64, simplified)

movq 8(%rax), %rsi

movq 16(%rax), %rdx

addq $32, %rax

movq -8(%rax), %rcx

movq -256(%rbp,%rdx,8), %rdx

addq -256(%rbp, %rsi, 8), %rdx # +

movq %rdx, -256(%rbp,%rcx,8)

movq (%rax), %rdx

jmpq *rdx

```

## The VM instruction add (here direct-threaded), compiled

```

compiled (x86_64, simplified)

movq 8(%rax), %rsi

movq 16(%rax), %rdx

addq $32, %rax

movq -8(%rax), %rcx

movq -256(%rbp,%rdx,8), %rdx

addq -256(%rbp,%rsi,8), %rdx # +

movq %rdx, -256(%rbp,%rcx,8)

movq (%rax), %rdx

jmpq *rdx

```

- the actual addition costs only one hardware instruction (the second addq, in black [which also includes one memory access]).

- Fallthru to the next VM instruction: three hardware instructions (*increment-load-jump*).

- The other five hardware instructions only serve to access VM registers (and on RISCs it's even worse).

## The VM instruction add (here direct-threaded), compiled

```

GNU C

label_add:

regs[insn[3].i]

= ( regs[insn[1].i]

+ regs[insn[2].i]);

insn += 4:

goto * insn->label;

```

```

compiled (x86 64, simplified)

movq 8(%rax), %rsi

movq 16(%rax), %rdx

addq $32, %rax

movq -8(%rax), %rcx

movq -256(%rbp,%rdx,8), %rdx

addq -256(%rbp, %rsi, 8), %rdx # +

movq %rdx, -256(%rbp,%rcx,8)

movq (%rax), %rdx

jmpq *rdx

```

- the actual addition costs only one hardware instruction (the second addg, in black [which also includes one memory access]).

- Fallthru to the next VM instruction: three hardware instructions (increment-load-jump).

## The VM instruction add (here direct-threaded), compiled

```

GNU C

label_add:

regs[insn[3].i]

= ( regs[insn[1].i]

+ regs[insn[2].i]);

insn += 4:

goto * insn->label;

```

```

compiled (x86 64, simplified)

movq 8(%rax), %rsi

movq 16(%rax), %rdx

addq $32, %rax

movq -8(%rax), %rcx

movq -256(%rbp,%rdx,8), %rdx

addq -256(%rbp, %rsi, 8), %rdx # +

movq %rdx, -256(%rbp,%rcx,8)

movq (%rax), %rdx

jmpq *rdx

```

- the actual addition costs only one hardware instruction (the second addg, in black [which also includes one memory access]).

- Fallthru to the next VM instruction: three hardware instructions (increment-load-jump).

- The other five hardware instructions only serve to access VM registers (and on RISCs it's even worse).

# (Direct-threaded) VM add: register indices and shifts

In the C code for VM instructions we access VM register contents with expressions such as regs [idx], where idx is usually insn[k]. i for some constant k.

$$regs + idx \cdot w$$

# (Direct-threaded) VM add: register indices and shifts

In the C code for VM instructions we access VM register contents with expressions such as regs [idx], where idx is usually insn[k]. i for some constant k.

Reading insn[k]. i into idx costs one load instruction (register plus a known constant offset). Loading regs [idx] is more

$$regs + idx \cdot w$$

## (Direct-threaded) VM add: register indices and shifts

In the C code for VM instructions we access VM register contents with expressions such as regs [idx], where idx is usually insn[k]. i for some constant k.

Reading insn[k]. i into idx costs one load instruction (register plus a known constant offset). Loading regs[idx] is more delicate: the address to load from is

$$regs + idx \cdot w$$

where w is the word size in bytes (4 on 32-bit machines, 8 on 64-bit machines). The multiplication requires a separate shift instruction on most RISC machines [plus possibly yet another instruction for summing regs and  $(idx \cdot w)$ : needed on RISC-V, MIPS, Alpha].

## (Direct-threaded) VM add: register indices and shifts

In the C code for VM instructions we access VM register contents with expressions such as regs [idx], where idx is usually insn[k]. i for some constant k.

Reading insn[k]. i into idx costs one load instruction (register plus a known constant offset). Loading regs[idx] is more delicate: the address to load from is

$$regs + idx \cdot w$$

where w is the word size in bytes (4 on 32-bit machines, 8 on 64-bit machines). The multiplication requires a separate shift instruction on most RISC machines [plus possibly yet another instruction for summing regs and  $(idx \cdot w)$ : needed on RISC-V, MIPS, Alpha].

Shifting at run time is silly: instead of keeping VM register indices in the VM program we can keep VM register offsets from regs, or in other words we can keep pre-shifted register indices.

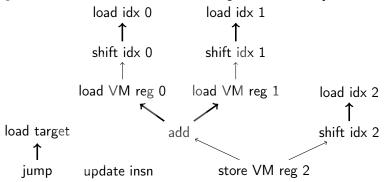

# (Direct-threaded) VM add: operation dependency graph

" $a \rightarrow b$ " means that a uses the result of b, so b is executed before a. Thick arrows mean high latencies ( $\sim 3\tau$ ).

[Register index shifts shown, offset sums to regs base not shown]

# (Direct-threaded) VM add: operation dependency graph

" $a \rightarrow b$ " means that a uses the result of b, so b is executed before a. Thick arrows mean high latencies ( $\sim 3\tau$ ).

[Register index shifts shown, offset sums to regs base not shown]

# (Direct-threaded) VM add: operation dependency graph

" $a \rightarrow b$ " means that a uses the result of b, so b is executed before a. Thick arrows mean high latencies ( $\sim 3\tau$ ).

[Register index shifts shown, offset sums to regs base not shown]

Two long dependency chains, each including two loads:  $load \leftarrow shift \leftarrow load \leftarrow add \leftarrow store. \sim 6\tau$  latency just from the loads, with ideal Instruction-Level Parallelism! In practice it will be worse.

# (Direct-threaded) VM add: operation dependency graph

" $a \rightarrow b$ " means that a uses the result of b, so b is executed before a. Thick arrows mean high latencies ( $\sim 3\tau$ ).

[Register index shifts shown, offset sums to regs base not shown]

Two long dependency chains, each including two loads:  $load \leftarrow shift \leftarrow load \leftarrow add \leftarrow store. \sim 6\tau$  latency just from the loads, with ideal Instruction-Level Parallelism! In practice it will be worse.

#### (Direct-threaded) VM b: operation dependency graph

Longest (and only) dependency chain  $load \leftarrow load \leftarrow jump$ . A VM unconditional branch has latency similar to a VM add; a VM b can easily be faster than a VM add if the hardware branch target predictor does its job.

Example AST Linear switch Threading Args Stacks Basics Specialization Replication No-threading Closing

#### (Direct-threaded) VM b: operation dependency graph

Longest (and only) dependency chain  $load \leftarrow load \leftarrow jump$ . A VM unconditional branch has latency similar to a VM add; a VM b can easily be faster than a VM add if the hardware branch target predictor does its job.

VMs and hardware machines can have very different performance profiles.

#### (Direct-threaded) VM b: operation dependency graph

Longest (and only) dependency chain *load*←*load*←*jump*. A VM unconditional branch has latency similar to a VM add; a VM b can easily be faster than a VM add if the hardware branch target predictor does its job.

VMs and hardware machines can have very different performance profiles.

[I've understood, too late to make the change before the GHM, that this is optimizable. Can you see how? Hint: b can have two arguments instead of one, at least in the memory representation of the program.

#### (Direct-threaded) VM b: operation dependency graph

Longest (and only) dependency chain load←load←jump. A VM unconditional branch has latency similar to a VM add; a VM b can easily be faster than a VM add if the hardware branch target predictor does its job.

VMs and hardware machines can have very different performance profiles.

[I've understood, too late to make the change before the GHM, that this is optimizable. Can you see how? Hint: b can have two arguments instead of one, at least in the memory representation of the program.

#### What if we used a stack instead of VM registers?

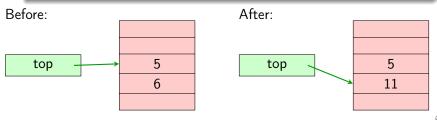

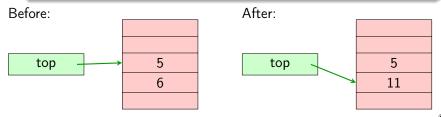

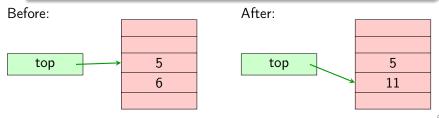

Stack-oriented VM instructions replace the top few elements of a stack with the result of an operation. For example stack\_add (zero arguments) could pop two elements (say, 5 and 6) from the stack and push their sum (11). This idea is about using stacks instead of VM registers, not just call stacks.

The authors of [Shi et al., 2005], in other works as well, argue from experimental data that direct-threaded register VMs are faster than direct-threaded stack VMs (same model I'm presenting here, stack code machine-translated to VM-register code with optimizations).

Unfortunately it's difficult to replicate their measurements. I wonder if their results still hold today, with our proportionally slower L1d caches and better branch predictors. [Still, stack code takes more instructions to do the same work, today like in 2005]

#### What if we used a stack instead of VM registers?

Stack-oriented VM instructions replace the top few elements of a stack with the result of an operation. For example stack\_add (zero arguments) could pop two elements (say, 5 and 6) from the stack and push their sum (11). This idea is about using stacks instead of VM registers, not just call stacks.

experimental data that direct-threaded register VMs are faster than direct-threaded l'm presenting here, stack code machine-translated to VM-register code with optimizations).

Unfortunately it's difficult to replicate their measurements. I wonder if their results still hold today, with our proportionally slower L1d caches and better branch predictors. [Still, stack code takes more instructions to do the same work, today like in 2005]

#### What if we used a stack instead of VM registers?

Stack-oriented VM instructions replace the top few elements of a stack with the result of an operation. For example stack\_add (zero arguments) could pop two elements (say, 5 and 6) from the stack and push their sum (11). This idea is about using stacks instead of VM registers, not just call stacks.

The authors of [Shi et al., 2005], in other works as well, argue from experimental data that direct-threaded register VMs are faster than direct-threaded stack VMs (same model I'm presenting here, stack code machine-translated to VM-register code with optimizations).

Unfortunately it's difficult to replicate their measurements. I wonder if their results still hold today, with our proportionally slower L1d caches and better branch predictors. [Still, stack code takes more instructions to do the same work, today like in 2005]

#### What if we used a stack instead of VM registers?

Stack-oriented VM instructions replace the top few elements of a stack with the result of an operation. For example stack\_add (zero arguments) could pop two elements (say, 5 and 6) from the stack and push their sum (11). This idea is about using stacks instead of VM registers, not just call stacks.

The authors of [Shi et al., 2005], in other works as well, argue from experimental data that direct-threaded register VMs are faster than direct-threaded stack VMs (same model I'm presenting here, stack code machine-translated to VM-register code with optimizations).

Unfortunately it's difficult to replicate their measurements. I wonder if their results still hold today, with our proportionally slower L1d caches and better branch predictors. [Still, stack code takes more instructions to do the same work, today like in 2005]

#### What if we used a stack instead of VM registers?

Stack-oriented VM instructions replace the top few elements of a stack with the result of an operation. For example stack\_add (zero arguments) could pop two elements (say, 5 and 6) from the stack and push their sum (11). This idea is about using stacks instead of VM registers, not just call stacks.

The authors of [Shi et al., 2005], in other works as well, argue from experimental data that direct-threaded register VMs are faster than direct-threaded stack VMs (same model I'm presenting here, stack code machine-translated to VM-register code with optimizations).

Unfortunately it's difficult to replicate their measurements. I wonder if their results still hold today, with our proportionally slower L1d caches and better branch predictors. [Still, stack code takes more instructions to do the same work, today like in 2005]

#### Naïve stack implementation

Suppose the VM has a stack in a hardware memory array, with a top-of-stack pointer in a hardware register. This is a zero-argument stack add VM instruction:

```

GNU C

label_stack_add:

top [-1] = top [-1] + top [0];

top --;

/* Fallthru code omitted, same as always. */

```

#### Naïve stack implementation

Suppose the VM has a stack in a hardware memory array, with a top-of-stack pointer in a hardware register. This is a zero-argument stack add VM instruction:

```

GNU C

label_stack_add:

top [-1] = top [-1] + top [0];

top --;

/* Fallthru code omitted, same as always. */

```

Example AST Linear switch Threading Args Stacks Basics Specialization Replication No-threading Closing

#### Naïve stack implementation

Suppose the VM has a stack in a hardware memory array, with a top-of-stack pointer in a hardware register. This is a zero-argument stack add VM instruction:

```

GNU C

label_stack_add:

top [-1] = top [-1] + top [0];

top --;

/* Fallthru code omitted, same as always. */

```

Two (independent) loads, one store. This looks better than our

Example AST Linear switch Threading Args Stacks Basics Specialization Replication No-threading Closing

### Naïve stack implementation

Suppose the VM has a stack in a hardware memory array, with a top-of-stack pointer in a hardware register. This is a zero-argument stack add VM instruction:

```

GNU C

label_stack_add:

top [-1] = top [-1] + top [0];

top --;

/* Fallthru code omitted, same as always. */

```

Two (independent) loads, one store. This looks better than our VM-register add: constant offsets from top, no index/offset loads.

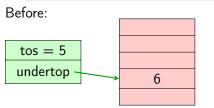

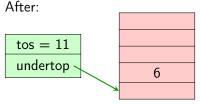

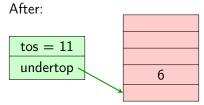

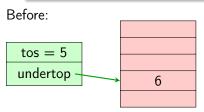

## Top-Of-Stack (TOS) optimization

We can do even better: keep the VM top stack *element* in a hardware register (the rest of the stack still in a hardware memory array), and an under-top *pointer* in a second hardware register.

```

GNU C

label_stack_add:

tos += undertop [0];

undertop --;

/* Fallthru code omitted, same as always. */

```

Only one load. Other VM instructions working only on the TOS (for example stack\_increment) require zero loads.

## Top-Of-Stack (TOS) optimization

We can do even better: keep the VM top stack *element* in a hardware register (the rest of the stack still in a hardware memory array), and an under-top *pointer* in a second hardware register.

```

GNU C

label_stack_add:

tos += undertop [0];

undertop --;

/* Fallthru code omitted, same as always. */

```

Only one load. Other VM instructions working only on the TOS (for example stack\_increment) require zero loads.

## Top-Of-Stack (TOS) optimization

We can do even better: keep the VM top stack element in a hardware register (the rest of the stack still in a hardware memory array), and an under-top *pointer* in a second hardware register.

```

GNU C

label_stack_add:

tos += undertop [0];

undertop --;

/* Fallthru code omitted, same as always. */

```

Only one load.

## Top-Of-Stack (TOS) optimization

We can do even better: keep the VM top stack *element* in a hardware register (the rest of the stack still in a hardware memory array), and an under-top *pointer* in a second hardware register.

```

GNU C

label_stack_add:

tos += undertop [0];

undertop --;

/* Fallthru code omitted, same as always. */

```

Only one load. Other VM instructions working only on the TOS (for example stack\_increment) require zero loads.

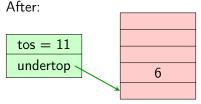

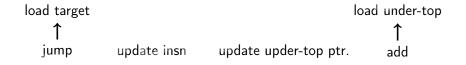

## (Direct-threaded) TOS-optimized stack\_add: operations

This includes the fallthru operations (update insn, load target, jump).

Very "flat"-looking graph with short dependency chains (max length 1). Not many operations.

## (Direct-threaded) TOS-optimized stack\_add: operations

This includes the fallthru operations (update insn, load target, jump).

Very "flat"-looking graph with short dependency chains (max length 1). Not many operations.

# (Direct-threaded) TOS-optimized stack\_add: operations

This includes the fallthru operations (update insn, load target, jump).

Very "flat"-looking graph with short dependency chains (max length 1). Not many operations.

### You've seen what every simple VMs does...

Nothing of what you saw up to here is new except for the removal of register *index shifts*, a minor optimization.

#### I want to make my VMs faster. In order of priority I need to:

- optimize VM register (and immediate argument) access [new]

- optimize fallthru [I learned the idea from [Ertl and Gregg, 2004], which builds upon previous work]

- remove insn and the VM program in memory [conceputally easy]

- optimize VM branches [my technique is new]

#### You've seen what every simple VMs does...

Nothing of what you saw up to here is new except for the removal of register *index shifts*, a minor optimization.

I want to make my VMs faster. In order of priority I need to:

- optimize VM register (and immediate argument) access [new]

- optimize fallthru [I learned the idea from [Ertl and Gregg, 2004], which builds upon previous work]

- remove insn and the VM program in memory [conceputally easy]

- optimize VM branches [my technique is new]

### You've seen what every simple VMs does...

Nothing of what you saw up to here is new except for the removal of register *index shifts*, a minor optimization.

I want to make my VMs faster. In order of priority I need to:

- optimize VM register (and immediate argument) access [new]

- optimize fallthru [I learned the idea from [Ertl and Gregg, 2004], which builds upon previous work]

- remove insn and the VM program in memory [conceputally easy]

- optimize VM branches [my technique is new]

### You've seen what every simple VMs does...

Nothing of what you saw up to here is new except for the removal of register *index shifts*, a minor optimization.

I want to make my VMs faster. In order of priority I need to:

- optimize VM register (and immediate argument) access [new]

- optimize fallthru [I learned the idea from [Ertl and Gregg, 2004], which builds upon previous work]

- remove insn and the VM program in memory [conceputally easy]

- optimize VM branches [my technique is new]

## You've seen what every simple VMs does...

Nothing of what you saw up to here is new except for the removal of register *index shifts*, a minor optimization.

I want to make my VMs faster. In order of priority I need to:

- optimize VM register (and immediate argument) access [new]

- optimize fallthru [I learned the idea from [Ertl and Gregg, 2004], which builds upon previous work]

- remove insn and the VM program in memory [conceputally easy]

- optimize VM branches [my technique is new]

### You've seen what every simple VMs does...

Nothing of what you saw up to here is new except for the removal of register *index shifts*, a minor optimization.

I want to make my VMs faster. In order of priority I need to:

- optimize VM register (and immediate argument) access [new]

- optimize fallthru [I learned the idea from [Ertl and Gregg, 2004], which builds upon previous work]

- remove insn and the VM program in memory [conceputally easy]

- optimize VM branches [my technique is new]

# Optimizing VM register access

VM registers should not be in hardware memory.

I want them in hardware registers (as long as they fit).

The problem: every time I do anything with

regs[e]

and the value of e isn't known at compile time I lose. GCC can't put any regs element in a specific hardware register, while there is even one regs[e] expression with unknown e — reading or writing.

The solution: never use regs[e] with a non-constant e; or even split regs into scalar variables reg\_0, reg\_1, reg\_2, ... and never take the address of those variables: writing "& regs\_i" is forbidder for every i.

# Optimizing VM register access

VM registers should not be in hardware memory.

I want them in hardware registers (as long as they fit).

The problem: every time I do anything with

regs[e]

and the value of e isn't known at compile time I lose. GCC can't put any regs element in a specific hardware register, while there is even one regs[e] expression with unknown e — reading or writing.

The solution: never use regs[e] with a non-constant e; or even split regs into scalar variables reg\_0, reg\_1, reg\_2, ... and never take the address of those variables: writing "& regs\_i" is forbidden for every i.

## Optimizing VM register access

VM registers should not be in hardware memory. I want them in hardware registers (as long as they fit).

The problem: every time I do anything with

and the value of e isn't known at compile time I lose. GCC can't put any regs element in a specific hardware register, while there is even one regs[e] expression with unknown e — reading or writing.

The solution: never use regs[e] with a non-constant e; or even split regs into scalar variables reg\_0, reg\_1, reg\_2, ... and never take the address of those variables: writing "& regs\_i" is forbidden for every i.

#### Let's look at a VM instruction such as add

[Here with register indices rather than offsets, just for simplicity: same point]

```

GNU C

label_add:

regs[insn[3].i] = regs[insn[1].i] + regs[insn[2].i];

insn += 4;

goto * insn->label;

```

Here regs is (always) indexed with insn[k].i, an index coming from the interpreted program!

And this pattern is very common across VM instructions.

#### Let's look at a VM instruction such as add

[Here with register indices rather than offsets, just for simplicity: same point]

```

GNU C

label_add:

regs[insn[3].i] = regs[insn[1].i] + regs[insn[2].i];

insn += 4;

goto * insn->label;

```

Here regs is (always) indexed with insn[k].i, an index coming from the interpreted program!

And this pattern is very common across VM instructions.

#### Let's look at a VM instruction such as add

[Here with register indices rather than offsets, just for simplicity: same point]

```

GNU C

label_add:

regs[insn[3].i] = regs[insn[1].i] + regs[insn[2].i];

insn += 4;

goto * insn->label;

```

Here regs is (always) indexed with insn[k].i, an index coming from the interpreted program!

And this pattern is very common across VM instructions.

#### Let's look at a VM instruction such as add

[Here with register indices rather than offsets, just for simplicity: same point]

```

GNU C

label_add:

regs[insn[3].i] = regs[insn[1].i] + regs[insn[2].i];

insn += 4;

goto * insn->label;

```

Here regs is (always) indexed with insn[k].i, an index coming from the interpreted program!

And this pattern is very common across VM instructions.

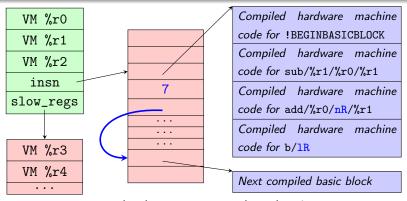

## VM instruction specialization

# A radical solution: forbid register indices/offsets as VM instruction arguments.

Remove the VM instruction add taking three index/offsets arguments from the interpreter. Instead there will be many specialized VM instructions:

```

add/%r0/%r0/%r0,

add/%r0/%r0/%r1,

add/%r0/%r1/%r0,

add/%r0/%r1/%r1, ...

add/%r1/%r1/%r1,

add/%r1/%r1/%r1,

```

Specialized instructions have no register-index/offset arguments; the specializations of our example's add have all **zero** arguments.

## VM instruction specialization

A radical solution: forbid register indices/offsets as VM instruction arguments.

Remove the VM instruction add taking three index/offsets arguments from the interpreter. Instead there will be many specialized VM instructions:

```

add/%r0/%r0/%r0.

add/%r0/%r0/%r1.

add/%r0/%r1/%r0.

add/%r0/%r1/%r1....

add/%r1/%r1/%r1.

add/%r0/%r0/%r2, ... Every possible combination.

```

A radical solution: forbid register indices/offsets as VM instruction arguments.

Remove the VM instruction add taking three index/offsets arguments from the interpreter. Instead there will be many *specialized* VM instructions:

```

add/%r0/%r0/%r0.

add/%r0/%r0/%r1.

add/%r0/%r1/%r0.

add/%r0/%r1/%r1....

add/%r1/%r1/%r1.

add/%r0/%r0/%r2, ... Every possible combination.

```

Specialized instructions have no register-index/offset arguments; the specializations of our example's add have all zero arguments.

Yes, I know that you have objections at this point.

Please give me one minute. I will address them.

#### Specialization is not manageable in human-written code:

Specialization is not manageable in human-written code:

- very long and redundant code

- fragile with respect to trivial details [how many programs slot to skip for fallthru? The number depends on how many arguments are VM registers]

## Where am I going?

Specialization is not manageable in human-written code:

- very long and redundant code

- fragile with respect to trivial details [how many programs slot to skip for fallthru? The number depends on how many arguments are VM registers]

The solution is machine-generating C code.

The new software I'm presenting is a code generator, automatically emitting C code for a VM from a human-written specification. Like Bison, and even more like Vmgen [Ertl et al., 2002], [Ertl, 2008].

- user-provided C code snippets for each unspecialized instruction

- convenient automatically-defined CPP macros to refer to (pre-specialization) arguments, and more

- fallthru code implicit for every VM instruction, automatically added by the generator

#### A VM instruction specification from the "Uninspired" VM (edited)

```

instruction add (?R, ?R, !R)

code

UNINSPIRED_ARGN2 = UNINSPIRED_ARGN0 + UNINSPIRED_ARGN1;

end

```

The new software I'm presenting is a code generator, automatically emitting C code for a VM from a human-written specification. Like Bison, and even more like Vmgen [Ertl et al., 2002], [Ertl, 2008].

- user-provided C code snippets for each unspecialized instruction

- convenient automatically-defined CPP macros to refer to (pre-specialization) arguments, and more

- fallthru code implicit for every VM instruction, automatically added by the generator

```

A VM instruction specification from the "Uninspired" VM (edited)

```

```

instruction add (?R, ?R, !R)

code

UNINSPIRED_ARGN2 = UNINSPIRED_ARGN0 + UNINSPIRED_ARGN1;

end

```

The new software I'm presenting is a code generator, automatically emitting C code for a VM from a human-written specification. Like Bison, and even more like Vmgen [Ertl et al., 2002], [Ertl, 2008].

- user-provided C code snippets for each unspecialized instruction

- convenient automatically-defined CPP macros to refer to (pre-specialization) arguments, and more

- fallthru code implicit for every VM instruction, automatically added by the generator

```

A VM instruction specification from the "Uninspired" VM (edited)

```

```

code

UNINSPIRED_ARGN2 = UNINSPIRED_ARGN0 + UNINSPIRED_ARGN1;

end

```

The new software I'm presenting is a code generator, automatically emitting C code for a VM from a human-written specification. Like Bison, and even more like Vmgen [Ertl et al., 2002], [Ertl, 2008].

- user-provided C code snippets for each unspecialized instruction

- convenient automatically-defined CPP macros to refer to (pre-specialization) arguments, and more

- fallthru code implicit for every VM instruction, automatically added by the generator

```

A VM instruction specification from the "Uninspired" VM (edited)

```

```

code

UNINSPIRED_ARGN2 = UNINSPIRED_ARGN0 + UNINSPIRED_ARGN1;

end

```

# The new software I'm presenting is a code generator, automatically

emitting C code for a VM from a human-written specification. Like Bison, and even more like Vmgen [Ertl et al., 2002], [Ertl, 2008].

- user-provided C code snippets for each unspecialized instruction

- convenient automatically-defined CPP macros to refer to (pre-specialization) arguments, and more

- fallthru code implicit for every VM instruction, automatically added by the generator

#### A VM instruction specification from the "Uninspired" VM (edited)

```

instruction add (?R, ?R, !R)

code

UNINSPIRED_ARGN2 = UNINSPIRED_ARGN0 + UNINSPIRED_ARGN1;

end

end

```

## Generated C code: general

- VM registers, or stacks (TOS-optimized or not), both, anything else implemented by the user

- user-specified data types (register classes: for example integer/pointer, floating point, vector, ...)

- several possible dispatching models

- switch-dispatching, direct threading, other models I'll show later:

- different performance profiles, identical behavior!

- lots of #ifdefs in the generated C code; choose dispatching model by compiling with -DDIRECT\_THREADING, . . .

- include custom C code from the user

- compatible with multi-threading and garbage collection, including exact pointer-finding [not just conservative as in Hans Bohem's GC]

## Generated C code: general

- VM registers, or stacks (TOS-optimized or not), both, anything else implemented by the user

- user-specified data types (register classes: for example integer/pointer, floating point, vector, ...)

- several possible dispatching models

- switch-dispatching, direct threading, other models I'll show later:

- different performance profiles, identical behavior!

- lots of #ifdefs in the generated C code; choose dispatching model by compiling with -DDIRECT\_THREADING, . . .

- include custom C code from the user

- compatible with multi-threading and garbage collection, including exact pointer-finding [not just conservative as in Han-Bohem's GC]

- VM registers, or stacks (TOS-optimized or not), both, anything else implemented by the user

- user-specified data types (register classes: for example integer/pointer, floating point, vector, ...)

- several possible dispatching models

- switch-dispatching, direct threading, other models I'll show later:

- different performance profiles, identical behavior!

- lots of #ifdefs in the generated C code; choose dispatching model by compiling with -DDIRECT\_THREADING, ...

# Generated C code: general

- VM registers, or stacks (TOS-optimized or not), both, anything else implemented by the user

- user-specified data types (register classes: for example integer/pointer, floating point, vector, ...)

- several possible dispatching models

- switch-dispatching, direct threading, other models I'll show later;

- different performance profiles, identical behavior!

- lots of #ifdefs in the generated C code; choose dispatching model by compiling with -DDIRECT\_THREADING, . . .

- include custom C code from the user

- compatible with multi-threading and garbage collection, including exact pointer-finding [not just conservative as in Hans Bohem's GC]

## Generated C code: general

- VM registers, or stacks (TOS-optimized or not), both, anything else implemented by the user

- user-specified data types (register classes: for example integer/pointer, floating point, vector, ...)

- several possible dispatching models

- switch-dispatching, direct threading, other models I'll show later:

- different performance profiles, identical behavior!

- lots of #ifdefs in the generated C code; choose dispatching model by compiling with -DDIRECT\_THREADING, ...

- include custom C code from the user

- compatible with multi-threading and garbage collection, including exact pointer-finding [not just conservative as in Hans Bohem's GC]

## Generated C code: portable

Making VMs portable with respect to different CPU architectures (also important for political reasons: free hardware as a prerequisite for privacy)

- Using C with as little assembly as possible, and not in user code (the assembly part is VM-independent, and already provided)

- even that little assembly is optional, only for better performance

- compiled VMs work comfortably even on "small" machines (32MB RAM is plenty; probably 8 or even 4MB is enough)

- (Compiling VMs is heavier, as you have guessed already

#### Generated C code: portable

#### Making VMs portable with respect to different CPU architectures (also important for political reasons: free hardware as a prerequisite for privacy)

- Using C with as little assembly as possible, and not in user code (the assembly part is VM-independent, and already provided)

Making VMs portable with respect to different CPU architectures (also important for political reasons: free hardware as a prerequisite for privacy)

- Using C with as little assembly as possible, and not in user code (the assembly part is VM-independent, and already provided)

- even that little assembly is optional, only for better performance

- Using C with as little assembly as possible, and not in user code (the assembly part is VM-independent, and already provided)

- even that little assembly is optional, only for better performance

- VMs behave identically, with or without assembly support

- Using C with as little assembly as possible, and not in user code (the assembly part is VM-independent, and already provided)

- even that little assembly is optional, only for better performance

- VMs behave identically, with or without assembly support

- direct threading with specialization is as portable as GCC

- Using C with as little assembly as possible, and not in user code (the assembly part is VM-independent, and already provided)

- even that little assembly is optional, only for better performance

- VMs behave identically, with or without assembly support

- direct threading with specialization is as portable as GCC

- switch-dispatching even more portable (no goto \*) (not yet implemented, but trivial)

### Generated C code: portable

- Using C with as little assembly as possible, and not in user code (the assembly part is VM-independent, and already provided)

- even that little assembly is optional, only for better performance

- VMs behave identically, with or without assembly support

- direct threading with specialization is as portable as GCC

- switch-dispatching even more portable (no goto \*) (not yet implemented, but trivial)

- compiled VMs work comfortably even on "small" machines (32MB RAM is plenty; probably 8 or even 4MB is enough)

- Using C with as little assembly as possible, and not in user code (the assembly part is VM-independent, and already provided)

- even that little assembly is optional, only for better performance

- VMs behave identically, with or without assembly support

- direct threading with specialization is as portable as GCC

- switch-dispatching even more portable (no goto \*) (not yet implemented, but trivial)

- compiled VMs work comfortably even on "small" machines (32MB RAM is plenty; probably 8 or even 4MB is enough)

- (Compiling VMs is heavier, as you have guessed already)

### Generated-code goodies

#### Along with the generated code you get:

- C API for dynamically generating and executing VM programs from your application

- driver with command-line options (main with convenient GNU command-line support for debugging and benchmarking)

- frontend: VM program parser and printer

- cross-compilation support

- disassembly to native or (via qemu-user) cross- code

- testsuite (even cross-, via qemu-user)

### Generated-code goodies

#### Along with the generated code you get:

- C API for dynamically generating and executing VM programs from your application

- driver with command-line options (main with convenient GNU command-line support for debugging and benchmarking)

- frontend: VM program parser and printer

- cross-compilation support

- disassembly to native or (via qemu-user) cross- code

- testsuite (even cross-, via qemu-user)

### Generated-code goodies

#### Along with the generated code you get:

- C API for dynamically generating and executing VM programs from your application

- driver with command-line options (main with convenient GNU command-line support for debugging and benchmarking)

- frontend: VM program parser and printer

- cross-compilation support

- disassembly to native or (via qemu-user) cross- code

- testsuite (even cross-, via qemu-user)

## Generated-code goodies

#### Along with the generated code you get:

- C API for dynamically generating and executing VM programs from your application

- driver with command-line options (main with convenient GNU command-line support for debugging and benchmarking)

- frontend: VM program parser and printer

- cross-compilation support

- disassembly to native or (via qemu-user) cross- code

- testsuite (even cross-, via qemu-user)

### Generated-code goodies

#### Along with the generated code you get:

- C API for dynamically generating and executing VM programs from your application

- driver with command-line options (main with convenient GNU command-line support for debugging and benchmarking)

- frontend: VM program parser and printer

- cross-compilation support

- disassembly to native or (via qemu-user) cross- code

- testsuite (even cross-, via qemu-user)

### Generated-code goodies

#### Along with the generated code you get:

- C API for dynamically generating and executing VM programs from your application

- driver with command-line options (main with convenient GNU command-line support for debugging and benchmarking)

- frontend: VM program parser and printer

- cross-compilation support

- disassembly to native or (via qemu-user) cross- code

- testsuite (even cross-, via qemu-user)

### Generated-code goodies

#### Along with the generated code you get:

- C API for dynamically generating and executing VM programs from your application

- driver with command-line options (main with convenient GNU command-line support for debugging and benchmarking)

- frontend: VM program parser and printer

- cross-compilation support

- disassembly to native or (via qemu-user) cross- code

- testsuite (even cross-, via qemu-user)

### Generated-code goodies

#### Along with the generated code you get:

- C API for dynamically generating and executing VM programs from your application

- driver with command-line options (main with convenient GNU command-line support for debugging and benchmarking)

- frontend: VM program parser and printer

- cross-compilation support

- disassembly to native or (via qemu-user) cross- code

- testsuite (even cross-, via gemu-user)

### VM specialized instructions: combinatorial explosion?

If we have *n* registers and *m* instructions (for example) all taking 3 register indices as arguments, specialized instructions are  $m \cdot n^3$ .

Yes, there are practical limits on how many VM registers of this kind you can have.

There are ways to reduce this growth and some optimizations I haven't implemented yet, but compiling a machine-generated VM is heavy. GCC can use GBs of RAM and take minutes to run when VM registers are many.

### VM specialized instructions: combinatorial explosion?

If we have *n* registers and *m* instructions (for example) all taking 3 register indices as arguments, specialized instructions are  $m \cdot n^3$ .

Yes, there are practical limits on how many VM registers of this kind you can have.

There are ways to reduce this growth and some optimizations I haven't implemented yet, but compiling a machine-generated VM is heavy. GCC can use GBs of RAM and take minutes to run when VM registers are many.

### Limiting combinatorial explosion

#### Some specialized instructions are useless or can be normalized:

- For example, addition is commutative: add/%r0/%r1/%r2 and add/%r1/%r0/%r2 do the same work, and we can keep only one. This halves the number of (commutative) specialized instructions.

- We can also rewrite every specialized instruction such as add/%ri/%rj/%rk

- into a two-specialized-instruction sequence

whenever  $j \neq k$ . [This is correct because add writes its third argument, but doesn't read it.] This rewrite can cut the number of specialized instructions from  $m \cdot n^3$  to  $m \cdot n^2$ .

Every specialized instruction which is not a rewrite target "doesn't

### Limiting combinatorial explosion

Some specialized instructions are useless or can be normalized:

- For example, addition is commutative: add/%r0/%r1/%r2 and add/%r1/%r0/%r2 do the same work, and we can keep only one. This halves the number of (commutative) specialized instructions.

- We can also rewrite every specialized instruction such as add/%ri/%ri/%rk

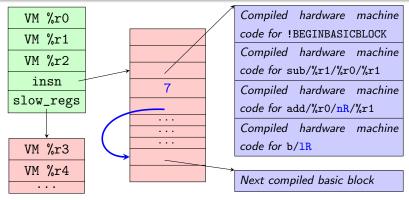

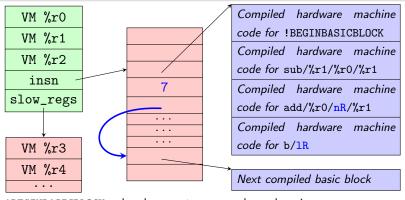

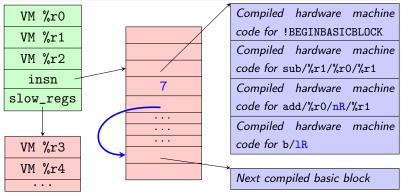

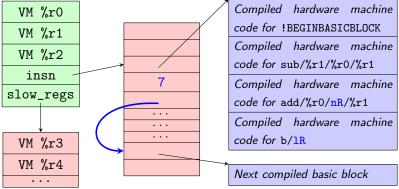

- into a two-specialized-instruction sequence